搜尋

- 09/10/2024

活動|環旭電子在「異質整合國際高峰論壇」分享尖端整合式電壓調節模組技術

(2024-09-10) 9月5日,SEMICON Taiwan 2024 國際半導體展,環旭電子技術長方永城在「異質整合國際高峰論壇」上分享了尖端的整合式電壓調節模組(IVRM)技術,這項創新技術將為人工智慧(AI)和機器學習(ML)的高效能運算提供動力。

伴隨著AI的崛起,異質整合技術引領未來發展。今年的SEMICON Taiwan 2024國際半導體展為期三天,針對異質整合技術與發展舉行了「2024異質整合國際高峰論壇」主題演講,邀請產學界重量級講者分享生成式AI如何驅動晶片製造轉型與製程技術優化,並探討透過最新的智慧製造技術擴大AI價值鏈的機遇與突破點。方永城在論壇中指出,無論是人工智慧或機器學習,特別是大規模AI伺服器,耗能巨大,被認為是能源吞噬者,因此需要找到更好的方法來提升效能。作為解決方案提供者,減少電力流失以及從晶片層面提高功率效率是我們關注的焦點。

高效能整合系統需要將高功率以高電流密度傳遞至負載點(POLs),而垂直傳遞高功率並將電源轉換更靠近負載點,縮短路徑是一種提高電源傳遞系統整體效率的可行方法。空間限制是另一個問題,電源需求越來越高,以升級從320W到400W的晶片組為例,320W需要8相設計,而400W則需要10相設計,如何將10相設計擠入8相的空間是一個挑戰。因此,我們想要實現一個垂直整合的解決方案。

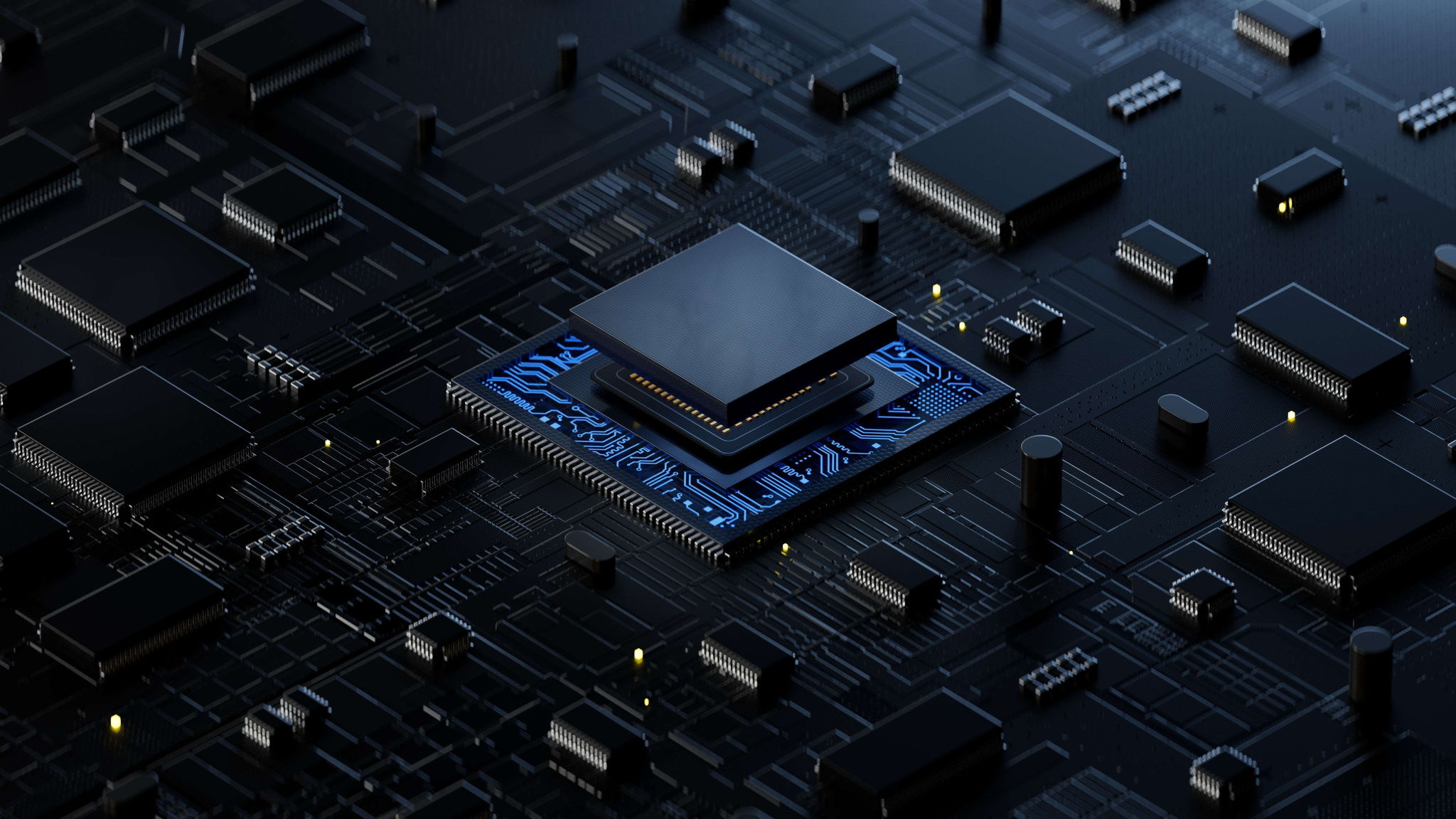

高效能運算(HPC)系統電源解決方案的發展,最開始是將電源元件獨立並排在電路板上。接著將多個元件整合到一個電源模組中,移到電路板下方,以縮短電流路徑。更進一步使用垂直推疊SiP技術整合的多階電壓調節模組,提高電源效率、密度、可靠性和空間利用率,以滿足不斷增長的高效能運算需求。

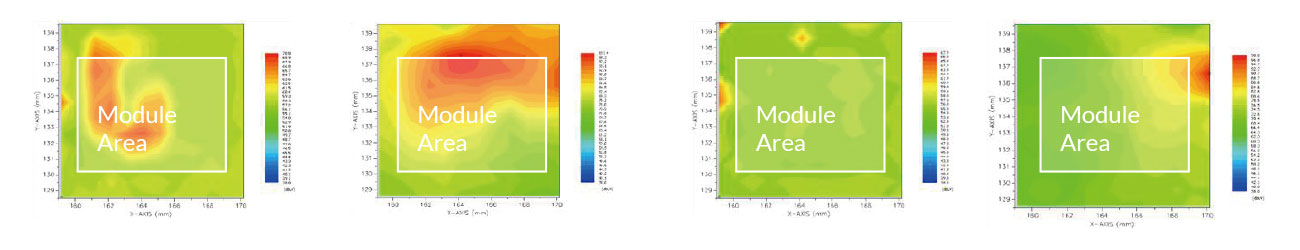

目前市面上有五種堆疊式電源模組,有的使用一個金屬夾,有的在一邊或四邊使用排針,或是加一個獨立的電路板,目的都是試著要解決高電流傳輸問題。無主電路板的垂直整合電源調節模組,可以實現多級電壓調節,即在同一晶片上完成多個電壓轉換的過程,直接將電壓調節模組放置在系統單晶片(SoC)下方,縮短電流流動的距離,並減少電流路徑上的銅損,提高系統的整體效率和性能。與過去獨立並列排在電路板上的方式相比,電流密度從0.4A/mm²增加50%至0.6A/mm²,並將佈線功耗從12%降低至6%。

透過垂直整合將元件堆疊縮短水平面積和降低模組高度,運用異質整合以及高密度封裝技術,在更小的空間內提高元件密度,並將晶片直接嵌入基板,減少連接層數和寄生電容,降低電阻和熱阻,實現提高性能、可靠性和降低功耗,這是未來整合式電壓調節模組發展的趨勢。

日月光投控旗下日月光的powerSiP™平台就是一個創新供電平台範例,可以減少訊號和傳輸損耗,同時解決目前存在的電流密度挑戰,實現垂直整合的多階電壓調節模組(VRM),提供更高的系統效率和更低的功耗。

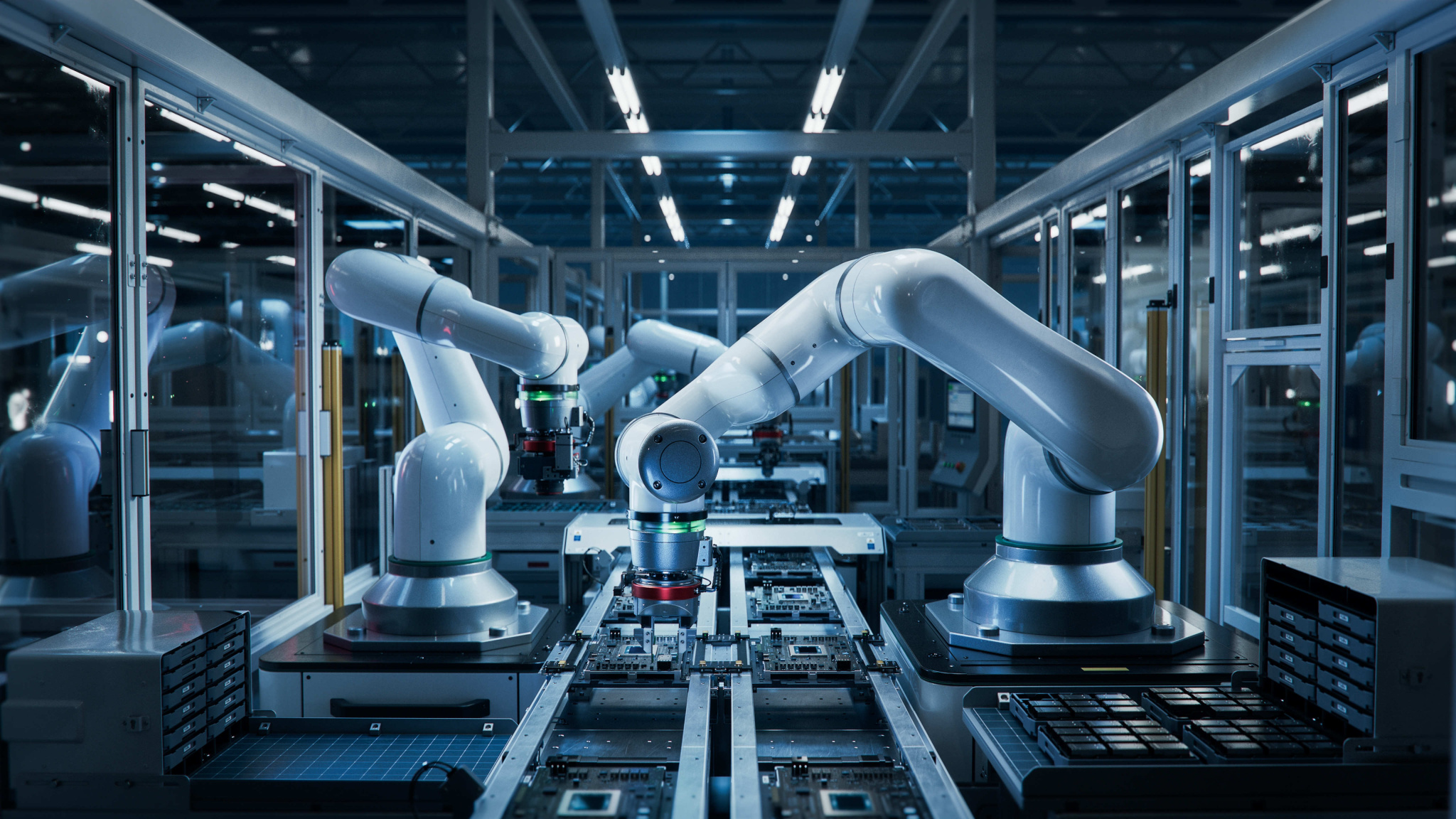

環旭電子MCC微小化創新研發中心的能力涵蓋將各種元件異質整合到複雜模組中,利用成熟的封裝成型技術,為客戶實現各種應用的靈活模組化。

最後,技術長方永城也代表公司參加ASE VP Dr. C.P. Hung主持的2024異質整合國際高峰論壇的專題,與imec的Dr. Eric Beyne、Intel的Dr. Debendra Das Sharma、Silicon Box的Dr. Byung Joon (BJ) Han和UMC的Mr. Kite Huang針對應對AI時代來臨的挑戰進行意見交流,強調必須利用AI工具,確保更高的效率、更好的時間管理和能源使用。

伴隨著AI的崛起,異質整合技術引領未來發展。今年的SEMICON Taiwan 2024國際半導體展為期三天,針對異質整合技術與發展舉行了「2024異質整合國際高峰論壇」主題演講,邀請產學界重量級講者分享生成式AI如何驅動晶片製造轉型與製程技術優化,並探討透過最新的智慧製造技術擴大AI價值鏈的機遇與突破點。方永城在論壇中指出,無論是人工智慧或機器學習,特別是大規模AI伺服器,耗能巨大,被認為是能源吞噬者,因此需要找到更好的方法來提升效能。作為解決方案提供者,減少電力流失以及從晶片層面提高功率效率是我們關注的焦點。

高效能整合系統需要將高功率以高電流密度傳遞至負載點(POLs),而垂直傳遞高功率並將電源轉換更靠近負載點,縮短路徑是一種提高電源傳遞系統整體效率的可行方法。空間限制是另一個問題,電源需求越來越高,以升級從320W到400W的晶片組為例,320W需要8相設計,而400W則需要10相設計,如何將10相設計擠入8相的空間是一個挑戰。因此,我們想要實現一個垂直整合的解決方案。

高效能運算(HPC)系統電源解決方案的發展,最開始是將電源元件獨立並排在電路板上。接著將多個元件整合到一個電源模組中,移到電路板下方,以縮短電流路徑。更進一步使用垂直推疊SiP技術整合的多階電壓調節模組,提高電源效率、密度、可靠性和空間利用率,以滿足不斷增長的高效能運算需求。

目前市面上有五種堆疊式電源模組,有的使用一個金屬夾,有的在一邊或四邊使用排針,或是加一個獨立的電路板,目的都是試著要解決高電流傳輸問題。無主電路板的垂直整合電源調節模組,可以實現多級電壓調節,即在同一晶片上完成多個電壓轉換的過程,直接將電壓調節模組放置在系統單晶片(SoC)下方,縮短電流流動的距離,並減少電流路徑上的銅損,提高系統的整體效率和性能。與過去獨立並列排在電路板上的方式相比,電流密度從0.4A/mm²增加50%至0.6A/mm²,並將佈線功耗從12%降低至6%。

透過垂直整合將元件堆疊縮短水平面積和降低模組高度,運用異質整合以及高密度封裝技術,在更小的空間內提高元件密度,並將晶片直接嵌入基板,減少連接層數和寄生電容,降低電阻和熱阻,實現提高性能、可靠性和降低功耗,這是未來整合式電壓調節模組發展的趨勢。

日月光投控旗下日月光的powerSiP™平台就是一個創新供電平台範例,可以減少訊號和傳輸損耗,同時解決目前存在的電流密度挑戰,實現垂直整合的多階電壓調節模組(VRM),提供更高的系統效率和更低的功耗。

環旭電子MCC微小化創新研發中心的能力涵蓋將各種元件異質整合到複雜模組中,利用成熟的封裝成型技術,為客戶實現各種應用的靈活模組化。

最後,技術長方永城也代表公司參加ASE VP Dr. C.P. Hung主持的2024異質整合國際高峰論壇的專題,與imec的Dr. Eric Beyne、Intel的Dr. Debendra Das Sharma、Silicon Box的Dr. Byung Joon (BJ) Han和UMC的Mr. Kite Huang針對應對AI時代來臨的挑戰進行意見交流,強調必須利用AI工具,確保更高的效率、更好的時間管理和能源使用。

跟緊產業脈動

隨時掌握第一手產業創新科技、應用與深度新聞

訂閱 USI 部落格

隨時掌握第一手產業創新科技、應用與深度新聞